要想从半导体工艺节点的发展中受益并非易事。伴随每一代全新工艺节点而来的是众多设计挑战和风险。7nm节点是所有领先晶圆厂目前能提供的最先进工艺。该工艺节点从根本上对基于容限的设计的基本假设提出了挑战。与此同时,它还能提高设计人员能够获得的功耗和性能极限。在不久的将来7nm节点会成为行业驱动力,因此设计人员正利用前期仿真技术从根本上重新思考他们的设计实现策略。

“在不久的将来7nm节点会成为行业驱动力,因此设计人员正利用前期仿真技术从根本上重新思考他们的设计实现策略。”

利用ANSYS RedHawk-CTA进行准确的芯片–封装热分析

功耗和性能一直是高级片上系统(SoC)半导体设计中两个相互矛盾的考虑因素。7nm工艺节点的优势是能够以更低的电源电压(低于500mV)运行,而且不会降低性能,主要原因在于每个晶体管的驱动电流变大了。此外,这些节点的漏电特性远低于平面CMOS晶体管。7nm工艺节点的这些关键特性使其非常适合帮助集成器件制造商(IDM)和无代工厂半导体公司开展高级SoC设计。

根据历史经验,迁移到更小的工艺节点都会减少单位面积内每个晶体管的成本。而在7nm工艺节点,几何微缩趋势已达到平衡,而且光刻掩膜的复杂性不断增加,使得每单位晶体管的成本显著高于前面几代的成本。

无代工厂的半导体公司需要利润更高或产量更大的产品来抵消7nm设计的成本。此外,芯片的性能必须显著增加产品本身的价值。在这种情况下,7nm芯片的失败成本非常高,无代工厂公司在采用这种新工艺节点时一定会权衡风险与回报之间的平衡。

7nm工艺的关键可靠性问题

挑战与风险

电源噪声收敛仍然是7nm设计的最大挑战之一。为了利用动态电源上电源电压的二次方尺寸缩小,设计团队推动极限发展,使工作电压降至470mV。与此同时,在过去几代工艺节点上阈值电压(VT)一直保持不变。更低的电源电压与几乎不变的阈值电压相结合,导致7nm节点的工作噪声容限快速减小。在这种情况下,传统的基于容限的压降验收方案很快失效。

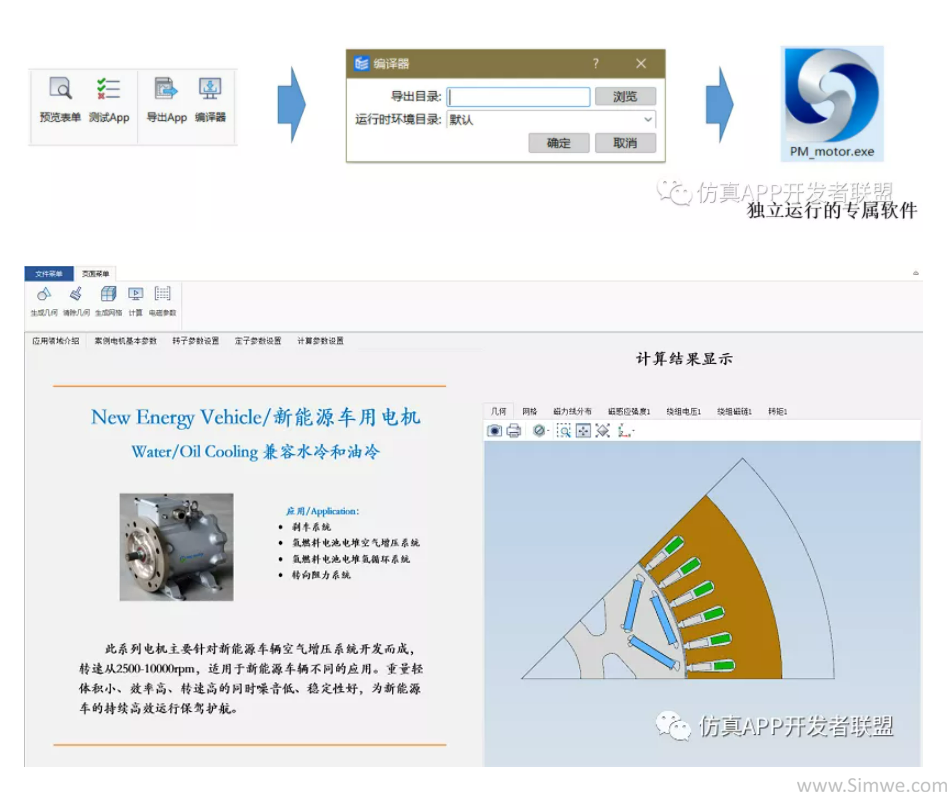

为降低电源噪声,需要在7nm节点采用全新的设计理念。选择正确的逻辑库、具有金属叠层的电源网格架构、时钟方案以及合适的IC封装,对于设计的抗干扰性有着深刻影响。为捕捉噪声引起的故障需要实现恰当的仿真覆盖范围,这个过程实际具有更加隐蔽的挑战。首先是设置鲁棒性的电源网格以满足所有容限要求,这是一个很容易犯的错误。这会对下游的时序和路由收敛造成影响,从而影响晶片尺寸。必须使用仿真支持的电源网格架构,以针对局部和全局开关故障覆盖所有工作模式。为了提高验收置信度,需要对数百种逻辑一致的情境进行特性分析,并对其中具有最佳覆盖条件的情境进行仿真。覆盖条件包含开关行为、峰值电流、有效电阻、时序余量或很多其他参数。鉴于当今SoC设计的复杂性,这个任务并非易事。ANSYS RedHawk-SC等平台可利用基于矢量或非矢量的方法来捕获设计薄弱点,从而对数百种情境进行特性分析。

利用ANSYS RedHawk-SC实现的多模式、多周期矢量覆盖范围

用于芯片–封装–系统收敛的ANSYS SeaScape平台

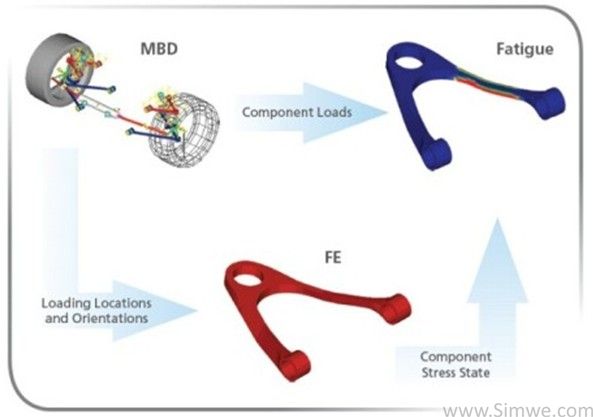

电迁移(EM)和热分析的可靠性仿真是7nm设计验收的另一个难题。FinFET器件架构从根本上限制了每个晶体管中翅片结构到硅衬底的热传导路径。与此同时,由于7nm工艺具有更高的金属密度,基极层与金属布线之间的垂直热耦合也会增加。这些热特性导致器件和金属局部自发热,加快器件寿命衰减并影响器件性能。

随着升级到每一代新的工艺节点,设计人员解决EM违规时所花费的时间不断增加,7nm也不例外。主要原因在于采用了最差情况温度的基于容限的EM验收方法。若采取过度设计,即利用更宽的金属和更多通孔来解决EM违规问题,会造成路由空间不足。通过利用ANSYS RedHawk-CTA进行热感知统计EM验收,设计人员就能节省宝贵的芯片面积,并减少在修复EM违规问题上所花费的时间。这能大幅降低延期风险。

器件老化和可变性是7nm工艺节点的另一个重要方面。设计人员需要了解负偏压温度不稳定性(NBTI)和热载流子注入(HCI)对器件老化和性能的影响,这是所有FinFET节点的一个重要检查事项。研究表明,信号概率与老化引起的性能劣化之间存在很强的关联。为获取该行为特性,设计人员需要在SoC级的多种工作负荷下建立NBTI感知库以及信号概率的详细模型。ANSYS Path FX 和ANSYS Variance FX 能够执行可变性感知以及老化感知的时序仿真,以提高7nm节点的验收置信度。

“在不久的将来7nm节点会成为行业驱动力,因此设计人员正利用前期仿真技术从根本上重新思考他们的设计实现策略。”

建模可用精度

由于7nm工艺具有更低的噪声容限,因此在建立基础IP和逻辑库的模型时不能降低精度。设计人员应该在较宽电压范围内确定标准单元的特性,以了解超低电压对电流消耗的影响。多位触发器(MBFF)应具有准确的位电流,并支持电流宿的空间分配。更大的模拟IP和存储器应具有准确的晶体管级细节,以实现正确的电流分配。此外,在进行7nm验收时,还必须准确建立片上供电网络的通道模型以及封装和电路板模型。片上提取工具应当支持多颜色感知的双重和三重曝光规则,并且经过代工厂认证。此外,封装建模应支持凸点级分辨率的全波精度,以捕获空间可变性。ANSYS RedHawk和ANSYS RedHawk-CTA这样的平台提供经过代工厂认证的提取规则,以及封装建模所需的精度。

对数千种情境进行快速设计探索

基于多种参数的临界矢量选择

时序、功能、电源噪声和可靠性收敛都是芯片确认过程中的不同阶段,通常采用独立的验收方案。在旧技术节点上,为这些确认步骤调整容限和采用超裕量设计的效果不错,不会造成很大影响。然而,对于16nm和7nm节点,在单个确认步骤上花费的时间显著增加,影响到实际的项目进度和成本。例如,在7nm节点上电源噪声与时序收敛的相关性显著提高。同样,自发热对EM或器件老化与时序收敛的相关性也有所提高。如果设计团队不采用新的方法,验证壁垒很快会带来进度和成本风险。ANSYS SeaScape等平台可提供快速的仿真覆盖并消除壁垒之间的分析差距,是有效避免7nm节点过度设计的必要工具。

ANSYS RedHawk-SC 平台

分析技术来救援

从大量仿真数据中创建可付诸行动的信息的能力对于7nm设计收敛至关重要。传统工具无法利用来自不同工具的指标来实现变更。例如,为了避免穿过高动态压降区域的低时序松弛路径,传统工具需要知道所有时序路径以及所有压降情境。同样,为了找到具有高峰值电流和高电阻路径的实例,传统工具需要知道有效电阻图以及实例负荷与当前模型的对比情况。在修复7nm问题时,具备上述分析能力的针对性设计修复方案比突击式方案要高效得多。设计团队可利用专用分析平台彻底改善设计收敛方法,例如采用可扩展型大数据架构、针对多物理场优化而构建的ANSYS SeaScape平台。

使用ANSYS SeaScape平台打破壁垒

总结

迁移到7nm工艺节点的过程中存在了各种风险与回报,从而给IC设计团队提出了艰巨的挑战。设计人员必须彻底改变实现和验证方法,通过创新的分析方法解决多物理场问题。打破电源噪声、时序、热和可靠性问题之间的壁垒,是唯一一种不会造成过度设计的可行方法。设计团队必须重新思考和建立设计过程,以完成势在必行的工艺迁移。